原文链接:https://www.cnblogs.com/Rainingday/p/14648048.html

查看stm32的SysTick中断的优先级,比外设中断优先级高吗?

默认SysTick中断优先级

1 //core_cm4.h 2 3 __STATIC_INLINE uint32_t SysTick_Config(uint32_t ticks) 4 { 5 if ((ticks - 1UL) > SysTick_LOAD_RELOAD_Msk) { return (1UL); } /* Reload value impossible */ 6 7 SysTick->LOAD = (uint32_t)(ticks - 1UL); /* set reload register */ 8 NVIC_SetPriority (SysTick_IRQn, (1UL << __NVIC_PRIO_BITS) - 1UL); /* set Priority for Systick Interrupt */ 9 SysTick->VAL = 0UL; /* Load the SysTick Counter Value */ 10 SysTick->CTRL = SysTick_CTRL_CLKSOURCE_Msk | 11 SysTick_CTRL_TICKINT_Msk | 12 SysTick_CTRL_ENABLE_Msk; /* Enable SysTick IRQ and SysTick Timer */ 13 return (0UL); /* Function successful */ 14 }第8行设置了SysTick中断的优先级,

#define __NVIC_PRIO_BITS 4 /*!< STM32F4XX uses 4 Bits for the Priority Levels */在看NVIC_SetPriority函数:NVIC_SetPriority对中断分了类,分内核中断和外设中断,内核外设中断枚举值小于0,普通外设>=0。其中,SysTick_IRQn = -1。

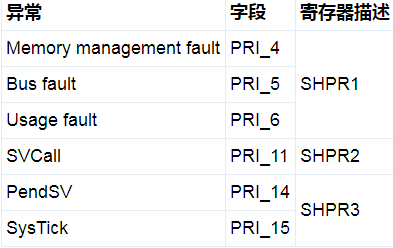

1 __STATIC_INLINE void NVIC_SetPriority(IRQn_Type IRQn, uint32_t priority) 2 { 3 if((int32_t)IRQn < 0) { 4 SCB->SHP[(((uint32_t)(int32_t)IRQn) & 0xFUL)-4UL] = (uint8_t)((priority << (8 - __NVIC_PRIO_BITS)) & (uint32_t)0xFFUL); 5 } 6 else { 7 NVIC->IP[((uint32_t)(int32_t)IRQn)] = (uint8_t)((priority << (8 - __NVIC_PRIO_BITS)) & (uint32_t)0xFFUL); 8 } 9 }因为SysTick属于内核外设,跟普通外设的中断优先级有些区别,并没有抢占优先级和子优先级的说法。在STM32F4中,内核外设的中断优先级由内核SCB这个外设的寄存器:SHPRx(x=1.2.3)来配置。有关SHPRx寄存器的详细描述可参考《Cortex-M4内核编程手册》4.4.8章节。下面我们简单介绍下这个寄存器。

SPRH1-SPRH3是一个32位的寄存器,但是只能通过字节访问,每8个字段控制着一个内核外设的中断优先级的配置。在STM32F4中,只有位7:4这高四位有效,低四位没有用到,所以内核外设的中断优先级可编程为:0~15,只有16个可编程优先级,数值越小,优先级越高。如果软件优先级配置相同,那就根据他们在中断向量表里面的位置编号来决定优先级大小,编号越小,优先级越高。

在SysTick_Config中,配置优先级为(1UL << __NVIC_PRIO_BITS) – 1UL),其中宏__NVIC_PRIO_BITS为4,那计算结果就等于15,可以看出SysTick此时设置的优先级在内核外设中是最低的。

SysTick和外设中断的优先级大小

但是,问题来了,如果我同时使用了systick和片上外设呢?而且片上外设也刚好需要使用中断,那systick的中断优先级跟外设的中断优先级怎么设置?会不会因为systick是内核里面的外设,所以它的中断优先级就一定比内核之外的外设的优先级高?

从《STM32中断应用概览》这章我们知道,外设在设置中断优先级的时候,首先要分组,然后设置抢占优先级和子优先级。而systick这类内核的外设在配置的时候,只需要配置一个寄存器即可,取值范围为0~15。既然配置方法不同,那如何区分两者的优先级?下面举例说明。

比如配置一个外设的中断优先级分组为2,抢占优先级为1,子优先级也为1,systick的优先级为固件库默认配置的15。当我们比较内核外设和片上外设的中断优先级的时候,我们只需要抓住NVIC的中断优先级分组不仅对片上外设有效,同样对内核的外设也有效。我们把systick的优先级15转换成二进制值就是1111(0b),又因为NVIC的优先级分组2,

那么前两位的11(0b)就是3,后两位的11(0b)也是3。无论从抢占还是子优先级都比我们设定的外设的优先级低。如果当两个的软件优先级都配置成一样,那么就比较他们在中断向量表中的硬件编号,编号越小,优先级越高。